CS 3889 Concurrency advanced module

A.R. Hurson 323 CS Building, Missouri S&T hurson@mst.edu

#### ♦ Outline

- Computation Gap

- Definition

- How to reduce computation gap

- Concurrency

- Definition

- Classifications

- Parallel systems

- Pipeline systems

- Multiprocessor systems

#### Computation Gap

- Computation gap is defined as the difference between computational power demanded by the application environments and computational capability of the existing computers.

- \*Today, one can find many applications which require orders of magnitude more computations than the capability of the most powerful computers.

## Computation Gap \*Computational requirements of some applications

It is estimated that the so called Problem Solving and Inference Systems require an environment with the computational power in the order of 100 MLIPS to 1 GLIPS (1 LIPS ≈ 100-1000 instructions).

#### Computation Gap

- Computational requirements of some applications

- Experiences in Fluid Dynamics have shown that the conventional super-computers can calculate steady 2-dimensional flow in minutes. However, conventional super-computers require up to 20 hours to handle time dependent 2-dimensional flow or steady 3dimensional flows on simple objects.

#### Computation Gap

- Computational requirements of some applications

- Numerical Aerodynamics Simulator requires an environment with a sustained speed of 1 billion FLOPS.

- Strategic Defense Initiative requires a distributed, fault tolerant computing environment with a processing rate of 600 MOPS.

- Computational requirements of some applications

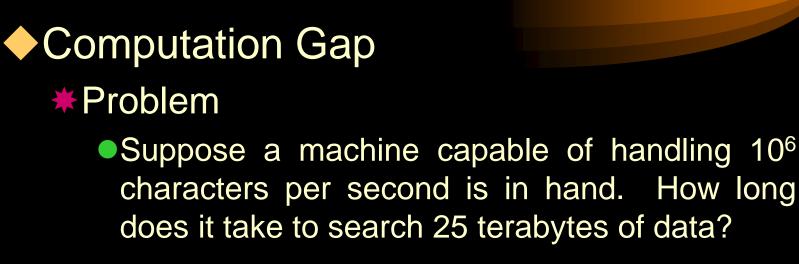

- U.S. Patent Office and Trademark has a database of size 25 terabytes subject to search and update.

- An angiogram department of a mid-size hospital generates more than 64 \* 10<sup>11</sup> bits of data a year.

- NASA's Earth Observing System will generate more than 11,000 terabytes of data during the 15-year time-period of the project.

- Computational requirements of some applications

- It was estimated that in 2002, 5 exabytes (1 exabyte= 10<sup>18</sup> bytes which is approximately equal to all words spoken by human beings) of new information was generated.

- The TREC database holds around 800 million static pages having 6 trillion bytes of plain text equal to the size of a million books.

- The Google system routinely accumulates millions of pages of new text information every week.

#### Computation Gap

#### \*Performance of some computers

| • CDC STAR-100                | 25-100 | MFLOPS |

|-------------------------------|--------|--------|

| <ul><li>DAP</li></ul>         | 100    | MFLOPS |

| <ul> <li>ILLIAC IV</li> </ul> | 160    | MFLOPS |

| • HEP                         | 160    | MFLOPS |

| CRAY-1                        | 25-80  | MFLOPS |

| • CRAY X-MP $(1)$             | 210    | MFLOPS |

| • CRAY X-MP(4)                | 840    | MFLOPS |

#### Computation Gap

#### \* Performance of some computers

| CRAY-2              | 250   | MFLOPS |

|---------------------|-------|--------|

| CDC CYBER 200       | 400   | MFLOPS |

| HitachiS-810(10)    | 315   | MFLOPS |

| HitachiS-810(20)    | 630   | MFLOPS |

| FujitsuFACOM VP-50  | 140   | MFLOPS |

| FujitsuFACOM VP-100 | 285   | MFLOPS |

| FujitsuFACOM VP-200 | 570   | MFLOPS |

| FujitsuFACOM VP-400 | 1,140 | MFLOPS |

#### Computation Gap

\*Performance of some computers

| ●NEC SX-1           | 570       | MFLOPS |

|---------------------|-----------|--------|

| ●NEC SX-2           | 1,300     | MFLOPS |

| ●IBM RP3            | 1,000     | MFLOPS |

| MPP 8-bit integer   | 1545-6553 | MIPS   |

| •MPP 12-bit integer | 795-4428  | MIPS   |

| •MPP 16-bit integer | 484-3343  | MIPS   |

| •MPP 32-bit FL      | 165-470   | MIPS   |

| MPP 40-bit FL       | 126-383   | MIPS   |

# Computation Gap \* Performance of some computers • NEC (Earth System) 35 tera FLOPS • IBM Blue Gene 70 tera FLOPS

#### The Top10 supercomputers

| Rank | Site                                                  | Computer/Year Vendor                                           | Country | Cores   | R <sub>max</sub><br>(Pflops) | R <sub>peak</sub><br>(Pflops) | Power<br>(MW) |

|------|-------------------------------------------------------|----------------------------------------------------------------|---------|---------|------------------------------|-------------------------------|---------------|

|      | RIKEN Advanced Institute for<br>Computational Science | K computer, SPARC64 VIIIfx<br>2.0GHz,/ 2011 Fujitsu            | Japan   | 548,352 | 8.162                        | 8.774                         | 9.899         |

| 2    | National Supercomputing<br>Center in Tianjin          | Tianhe-1A - NUDT / 2010 NUDT                                   | China   | 186,368 | 2.566                        | 4.701                         | 4.040         |

| 3    | Ũ                                                     | Jaguar - Cray XT5-2.6 GHz /<br>2009 Cray Inc.                  | USA     | 224,162 | 1.759                        | 2.331                         | 6.951         |

| 4    | National Supercomputing<br>Centre in Shenzhen         | Nebulae - Dawning TC3600<br>Blade/ 2010 Dawning                | China   | 120,640 | 1.271                        | 2.984                         | 2.580         |

| 5    | GSIC Center, Tokyo Institute<br>of Technology         | TSUBAME 2.0/2010 NEC/HP                                        | Japan   | 73,278  | 1.192                        | 2.288                         | 1.399         |

| 6    | DOE/NNSA/LANL/SNL                                     | Cielo - Cray XE6 8-core 2.4 GHz<br>/2011Cray Inc.              | USA     | 142,272 | 1.110                        | 1.365                         | 3.980         |

| 7    | NASA/Ames Research<br>Center/NAS                      | Pleiades - 2.93 Ghz,/ 2011 SGI                                 | USA     | 111,104 | 1.088                        | 1.315                         | 4.102         |

| 8    | DOE/SC/LBNL/NERSC                                     | Hopper - Cray XE6 12-core 2.1<br>GHz / 2010 Cray Inc.          | USA     | 153,408 | 1.054                        | 1.289                         | 2.910         |

| 9    | Ũ                                                     | Tera-100 - Bull bullx super-node<br>S6010/S6030 / 2010 Bull SA | France  | 138,368 | 1.050                        | 1.255                         | 4.590         |

| 10   | DOE/NNSA/LANL                                         | Roadrunner - 3.2 Ghz /2009 IBM                                 | USA     | 122,400 | 1.042                        | 1.376                         | 2.346         |

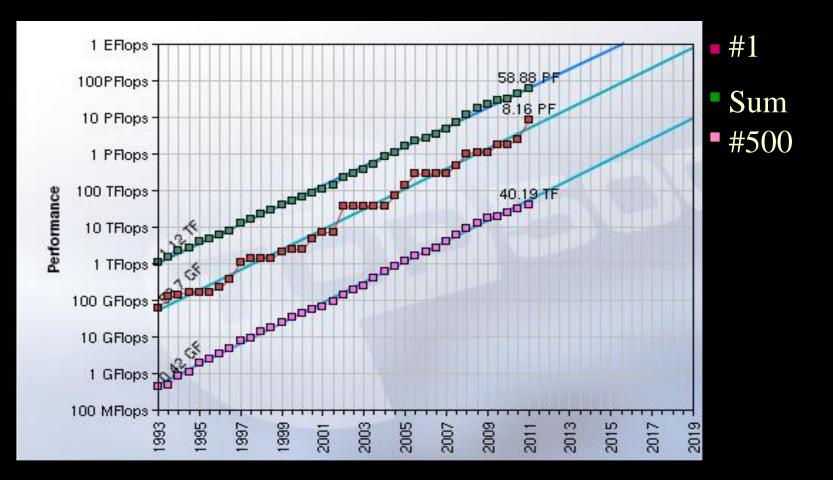

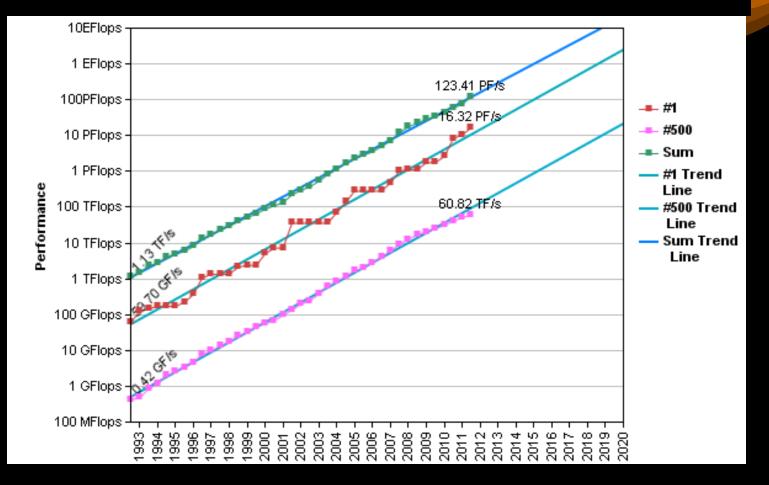

#### Trend in Supercomputer technology

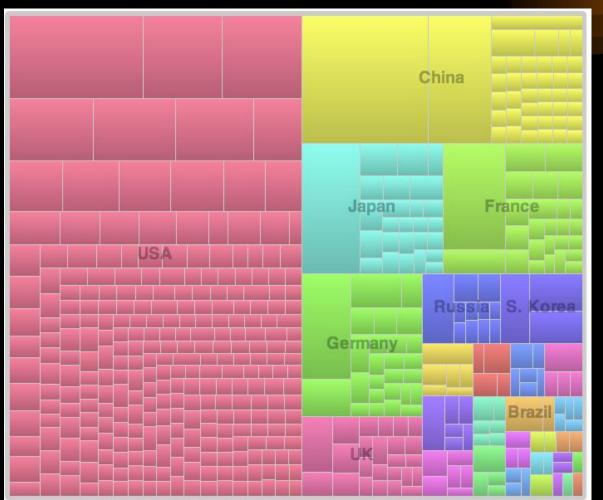

#### **Countries Share**

Absolute Counts US: 274 China: 41 Germany: 26 Japan: 26 France: 26 UK: 25

#### *Concurrency* Trend in Supercomputer technology (June 2012)

#### Rapid change in Countries Share

| Countries        | Count | Share % | Rmax Sum (GF) | Rpeak Sum (GF) | Processor Sum           |

|------------------|-------|---------|---------------|----------------|-------------------------|

| Australia        | 6     | 1.20 %  | 400406        | 552142         | 40344                   |

| <u>Austria</u>   | 2     | 0.40 %  | 188670        | 243386         | 26172                   |

| <u>Belgium</u>   | 2     | 0.40 %  | 83840         | 151472         | 16704                   |

| <u>Brazil</u>    | 2     | 0.40 %  | 269730        | 330445         | 37184                   |

| <u>Canada</u>    | 8     | 1.60 %  | 640129        | 890598         | 82684                   |

| <u>China</u>     | 61    | 12.20 % | 7136315       | 14331013       | 881832                  |

| <u>Denmark</u>   | 2     | 0.40 %  | 198408        | 260395         | 22218                   |

| <u>Finland</u>   | 2     | 0.40 %  | 117858        | 180690         | 18640                   |

| France           | 25    | 5.00 %  | 3180744       | 4100571        | 454928                  |

| Germany          | 30    | 6.00 %  | 3242111       | 4181323        | 568952                  |

| <u>India</u>     | 2     | 0.40 %  | 187910        | 242995         | 18128                   |

| Ireland          | 1     | 0.20 %  | 40495         | 76608          | 7200                    |

| Israel           | 2     | 0.40 %  | 135361        | 280436         | 23928                   |

| <u>Italy</u>     | 5     | 1.00 %  | 471746        | 748248         | 42080                   |

| Japan            | 26    | 5.20 %  | 11182236      | 13641290       | 832838                  |

| Korea, South     | 4     | 0.80 %  | 950833        | 1126280        | 123384                  |

| Netherlands      | 1     | 0.20 %  | 50924         | 64973          | 3456                    |

| <u>Norway</u>    | 1     | 0.20 %  | 40590         | 51060          | 5550                    |

| Poland           | 5     | 1.00 %  | 315075        | 448204         | 44274                   |

| <u>Russia</u>    | 12    | 2.40 %  | 1341586       | 2290994        | 115120                  |

| Saudi Arabia     | 4     | 0.80 %  | 359240        | 414841         | 81920                   |

| <u>Singapore</u> | 2     | 0.40 %  | 94073         | 144562         | 13192                   |

| <u>Spain</u>     | 2     | 0.40 %  | 135860        | 197696         | 14160                   |

| <u>Sweden</u>    | 5     | 1.00 %  | 489530        | 661642         | 75280                   |

| Switzerland      | 4     | 0.80 %  | 317895        | 383373         | 49480                   |

| <u>Taiwan</u>    | 2     | 0.40 %  | 220504        | 313570         | 32148                   |

| United Kingdom   | 27    | 5.40 %  | 1872107       | 2806546        | 260572                  |

| United States    | 255   | 51.00 % | 25265849      | 36064596       | 58037 <mark>55</mark> 6 |

As of June 2013, Tianhe-2 (Milky Way-2) (will be deployed at the National Supercomputer Center in Guangzho, China, by the end of the year) is the fastest super computer with theoretical peak performance of 54.9 PF/s (Linpack Performance of 33.8 PF/s). It is composed of 3,120,000 cores, consuming 17,808 kW.

Titan, a Cray XK7 system installed at the U.S. Department of Energy's (DOE) Oak Ridge National Laboratory and previously the No. 1 system, is now ranked No. 2. Titan achieved 17.59 petaflop/s on the Linpack benchmark using 261,632 of its NVIDIA K20x accelerator cores. Titan is one of the most energy efficient systems on the list, consuming a total of 8.21 MW and delivering 2,143 Mflops/W.

Sequoia, an IBM BlueGene/Q system installed at DOE's Lawrence Livermore National Laboratory, also dropped one position and is now the No. 3 system. Sequoia was first delivered in 2011 and has achieved 17.17 petaflop/s on the Linpack benchmark using 1,572,864 cores. Sequoia is also one of the most energy efficient systems on the list, consuming a total of 7.84 MW and delivering 2,031.6 Mflops/W.

$$\frac{25 * 10^{-12}}{10^{-6}} = 25 * 10^{-6} \text{ sec.} \approx 4 * 10^{-5} \text{ min.} \approx 7 * 10^{-3} \text{ Hours} \approx 290 \text{ days}$$

\*NOT PRACTICAL!

\*WHAT ARE THE SOLUTIONS?

Computation Gap — How to reduce it?

\* Reduce the amount of needed computations.

\* Improve the speed of the computers:

Physical Speed

Logical Speed

Computation Gap — Fewer Computation

\*Advances in Software Technology and Algorithms

- Since the early days of computers, the development of software support to maximize hardware utility has stimulated much research.

- Software systems were developed to tailor the embedded hardware features of a system to a specific application.

Computation Gap — Fewer Computation

\*Advances in Software Technology and Algorithms

Various data structure techniques can be used in order to achieve a higher performance.

Different algorithms can be developed to improve performance.

Computation Gap — Fewer Computation

\*Advances in Software Technology and Algorithms

A compiler equipped with an optimizer routine improves the performance during the runtime by creating an efficient target language program.

Computation Gap — Fewer Computation

\*Advances in Software Technology and Algorithms

> • A vectorized and parallelized compiler can enhance the performance by detecting the parallelism in an application program and rearranging the instructions in the object program to allow the simultaneous execution of independent instructions or block of instructions on the target machine, during the run time.

## Computation Gap — Physical Speed \*Advances in Technology

Transition from vacuum tubes to VLSI has made it possible to reduce the gate switching delay and size, and to increase the reliability of the hardware components.

#### Computation Gap — Physical Speed

#### \*Advances in Technology

Within the period of 1940-1980 the processor speed has been increased by more than four orders of magnitude, and logic circuit size and memory cell size have been reduced by factors of 500 and 6400, respectively.

#### Computation Gap — Physical Speed

#### Advances in Technology

- In 1944, a basic operation was executed in 333 msec.

- About 8 years later, in 1950s, due to the advances in technology, the same basic operation was executed in 282 µsec.

- In the early 1960s, again, because of the advances in technology, it took 300  $\eta$ sec to perform the same operation.

#### Computation Gap — Physical Speed Advances in Technology Is it possible to handle the same basic operation in 300 pico sec? For the period of 40s-60s, performance (speed) improvement due to the advances in technology has been at the rate of 10<sup>3</sup> per decade. Should we expect the same improvement rate forever?

30

# Computation Gap — Physical Speed Advances in Technology In 1970, Intel introduced the first single chip microprocessor, the Intel 4004. It had 2,600 manually placed transistors with clocking frequency of 100 KHz. Intel 4004 packed as much computing power as the ENIAC.

#### Computation Gap — Physical Speed Advances in Technology Limitations Speed of Light and Distance • Light travels $12 \times 10^9$ inch per sec. = 12 inch per nsec. In 300 pico sec. light travels 4 inches. Therefore, in a hardware unit (basic operation), if the total signal propagation distance is more than 4 inches then it is impossible to execute

the same basic operation in 300 pico seconds.

32

| Year                                                                             | 1947                              | 1950                                | 1961                                            | 1966                                 | 1971                            | 1980                                                      | 1985                                              | 1990       |

|----------------------------------------------------------------------------------|-----------------------------------|-------------------------------------|-------------------------------------------------|--------------------------------------|---------------------------------|-----------------------------------------------------------|---------------------------------------------------|------------|

| Technolgy                                                                        | Invention<br>of the<br>Transistor | Discrete<br>Components              | SSI                                             | MSI                                  | LSI                             | VLSI                                                      | ULSI*                                             | GSI**      |

| Approximate<br>number of<br>transistors<br>per chip in<br>commercial<br>products | 1                                 | 1                                   | 10                                              | 100-<br>1000                         | 1000-<br>20,000                 | 20,000-<br>500,000                                        | >500,000                                          | >1,000,000 |

| Typical<br>Products                                                              | -                                 | Junction<br>Transistor<br>and Diode | Planar<br>Devices,<br>Logic Gates<br>Flip-Flops | Counters,<br>Multiplexers,<br>Adders | 8-bit<br>Microproc.<br>ROM, RAM | 16 & 32-bit<br>Microproc.<br>Sophisticated<br>Peripherals | Special<br>Processors<br>Real Time<br>Image Proc. | ?          |

\* Ultra Large Scale Integration.

\*\* Giant Scale Integration

# Computation Gap — Physical Speed \* Advances in Technology Advances in technology reduce the circuit switching delay and miniaturize the hardware circuits. Nevertheless, it cannot transfer signals faster than the speed of light, and

cannot eliminate the distance.

### Computation Gap — Physical Speed \*Advances in Technology

In the late 1960s, Moore predicted that component density on a chip was quadrupling every three or four years. However, as advances in technology approach the limit, the Moore's law is no longer applicable.

Computation Gap — Logical Speed

\*One can take two general approaches to improve the logical speed of the system:

Architectural advances of the traditional uniprocessor systems,

Concurrency

Computation Gap — Logical Speed

\*Architectural advances of uni-processor system

- In this case, one has to look at the existing bottlenecks in a uni-processor systems and make an attempt to reduce these bottlenecks.

- As we discuss before access gap is one of the bottlenecks of the traditional uni-processor systems.

Computation Gap — Logical Speed

\*Architectural advances of uni-processor system

Access gap is defined as the time difference between the CPU cycle time and the main

memory cycle time.

#### Computation Gap — Logical Speed

\*Architectural advances of uni-processor system

- Access gap problem was created by the advances in technology. In fact, in early computers such IBM 704, CPU and main memory cycle time were identical - i.e., 12 µsec.

- IBM 360/195 had the logic delay of 5 ηsec per stage, the CPU cycle time of 54 ηsec and the main memory cycle time of .756 µsec.

- CDC 7600 had the CPU and main memory cycle time of 27.5 ηsec and .275 µsec, respectively.

## Computation Gap — Logical Speed Concurrency

To overcome the technological limitations, computer designers have long been attracted to techniques that are classified under the term of Concurrency.

## Computation Gap — Logical Speed \*Concurrency

- Concurrency is a generic term which defines the ability of the computer hardware to simultaneously execute many actions at any instant.

- Within this general term are several well recognized techniques such as Parallelism, Pipelining, and Multiprocessing.

## Computation Gap — Logical Speed Concurrency

- These techniques have the same origin and are often hard to distinguish, in practice they are different in their general approach.

- In parallelism concurrency is achieved by replicating the hardware structure many times, while pipelining takes the approach of splitting the function to be performed into smaller pieces and allocating separate hardware to each piece.

#### Computation Gap — Logical Speed

#### Concurrency

- To develop an understanding about concurrency, let us look at several architectural models. As a reminder, an instruction cycle is composed of these phases:

- I-fetch: to fetch the next instruction and update the program counter.

#### **I-decode**: to decode the instruction and fetch operand(s).

**I**-execute: to execute the instruction.

\*Assume that  $T_{I-fetch} = T_{I-decode} = T_{I-execute} = t$

# Computation Gap — Concurrency Classification Different researchers made an attempt to classify the concurrent space. This includes: Feng's Classification Flynn's Classification Handler's Classification In this course we will concentrate on Flynn's classification.

## Computation Gap — Concurrency \*Flynn's classification Flynn has classified the concurrent space according to the multiplicity of instruction and data streams

I = {Single Instruction stream, Multiple Instruction stream} D = {Single Data stream, Multiple Data stream}

### Computation Gap — Concurrency \*Flynn's classification

- The cartesian product of the two aforementioned sets will define four different classes:

- MISD

- MIMD

#### Computation Gap — Concurrency

In this course, concurrent space is classified into two groups:

- Control Flow

- Data Flow

Computation Gap — Concurrency

\*In the control flow model of computation, execution of an instruction activates the execution of the next instruction.

\*In the data flow model of computation, availability of the data activates the

execution of the next instruction(s).

#### Computation Gap — Concurrency

- Within the scope of the control flow systems we distinguish three sub-classes:

- Parallel Systems

- Pipeline Systems

- Multiprocessors

- This distinction is due to the exploitation of concurrency and the interrelationships among the control unit, processing elements and memory modules in each group.

Computation Gap — Parallel Systems

\*These systems are the natural extension of parallel ALU processors, where concurrency is exploited through a collection of identical and independent processing elements controlled by the same control unit.

Computation Gap — Parallel Systems

\*According to Flynn's classification these systems are classified as SIMD organization.

\*Parallel systems are synchronous organizations, scalable, and offer a good degree of fault tolerance.

Computation Gap — Parallel Systems

\* Parallel systems can be further classified as:

• Ensemble Processors

• Array Processors

• Associative Processors

#### Computation Gap — Parallel Systems

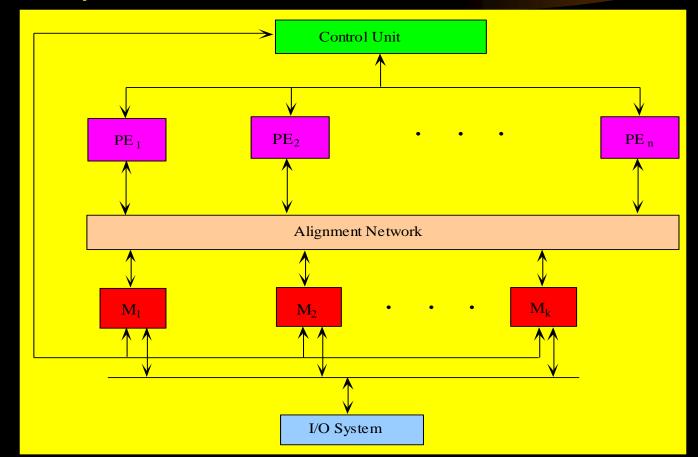

- Ensemble Processors had very limited capability and flexibility. Because of these limitations this class mainly became a conceptual class.

- It is an extension of a conventional uniprocessor system.

- It is a collection of N processing elements and N memory modules under the control of a single control unit.

## Computation Gap — Parallel Systems \*Ensemble Processors

- Each processing element consists of an ALU, a set of local registers and very limited local control capability.

- There exist no direct communication paths among processing elements.

- There exist fixed interconnections among processing elements and memory modules.

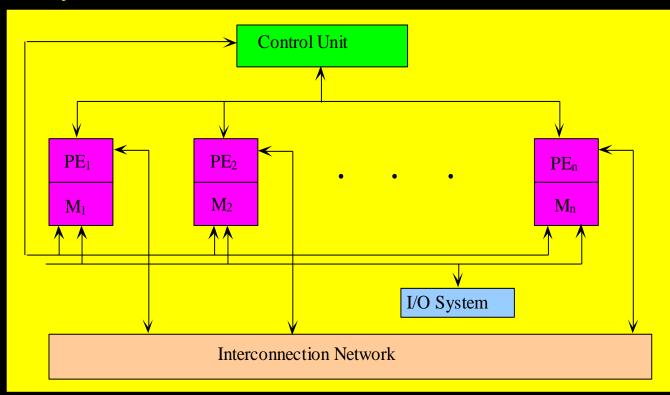

## Computation Gap — Parallel Systems \*Array of Processors

- It is composed of N identical processing elements under the control of a single control unit and a number of memory modules.

- Processing units and memory elements communicate with each other through an interconnection network.

- Complexity of the control unit is at the same level of the uniprocessor system.

## Computation Gap — Parallel Systems \*Array of Processors

- Control unit is a computer with its own high speed registers, local memory and arithmetic logic unit.

- The main memory is the aggregate of the memory modules.

- Control and scalar type instructions are executed in the control unit.

- Vector instructions are performed in the processing elements.

#### Computation Gap — Parallel Systems

#### \*Array of Processors

- Array processors can be further classified based on complexity of the processing elements or the processors memory modules relationships:

- Processing element complexity

- Single-bit processors (connection machine)

- Multi-bit processors (ILLIAC IV)

- Processor-memory interconnection

- Global memory organization (BSP)

- Dedicated memory organization (ILLIAC IV)

#### Computation Gap — Parallel Systems

\* Array of Processors — Global Memory Organization

#### Computation Gap — Parallel Systems

\* Array of Processors — Dedicated Memory Organization

59

#### Questions

- \*Compare and contrast single-bit and multi-bit array processor organizations against each other.

- Compare and contrast global memory and dedicated memory array processor organizations against each other.

- Discuss the problem(s) which degrade the performance of an array processor the most.

## Computation Gap — Parallel Systems \*Array of Processors

- Data structuring and detection of parallelism in a program are the major bottlenecks in an array processor organization.

- Operations such as X(i) = A(i) \* B(i) 1 ≤ i ≤ n could be executed in parallel, if the elements of the arrays A and B are distributed properly among the processors or memory modules i<sup>th</sup> processor is assigned the task of computing X(i).

Computation Gap — Parallel Systems \*Array of Processors — Example \*Compute are two one  $Y = \sum_{i=1}^{N} A(i) * B(i)$ where A and B dimensional arrays of N elements, and elements of A and B are properly distributed among processors - assume a dedicated organization.

Computation Gap — Parallel Systems

\*Array of Processors — Example

The product terms are generated in parallel.

Additions will be performed in iterations.

Speed up factor (S) then is:

$$S = \frac{2N-1}{1+\log_2 N} \approx \left(\frac{N}{\log_2 N}\right)$$

at the expense of a poor resource utilization(why)?

## Computation Gap — Parallel Systems \*Associative Processors

- An associative processor is defined as an associative memory capable of performing arithmetic and logic operations.

- Within this scope, then, an associative computer is defined as a system that uses an associative memory or associative processor as an essential component for storage or processing, respectively.

#### Computation Gap — Parallel Systems

#### **\***Associative Processors

- The main motivations for the application of associative processing are:

- reducing the semantic gap and bottleneck in the conventional systems, and

- increasing the performance due to the parallel nature of the operations at the storage level and elimination of address computation.

#### Computation Gap — Multiprocessor Systems

- Multiprocessor systems are the nature extension of parallel systems (justify this?)

- The attribute that characterizes a multiprocessor system is the sharing of a global memory by several independent processing units making up the system.

#### Computation Gap — Multiprocessor Systems

- Two arguments justify a multiprocessor organization:

- Higher throughput: due to the ability to overlap both computation intensive and I/O intensive tasks among independent processors in the system.

- Existence of a large class of problems that can be split up into a number of smaller and independent tasks.

#### Computation Gap — Multiprocessor Systems

- \*A multiprocessor system contains two or more processing units, each with its own control unit. Processors can be homogeneous or heterogeneous.

- \* Processing units are not highly specialized.

- Processing units share a main memory that usually consists of several independently accessible modules.

#### Computation Gap — Multiprocessor Systems

\*Besides a common memory, processing units usually share other resources such as I/O channels and devices.

The whole system is under the control of a single integrated operating system.

#### Computation Gap — Multiprocessor Systems

- Multiprocessor systems can be grouped into two classes:

- Tightly Coupled: shared memory modules are separated from processors by an interconnection network or a multiport interface.

- The memory access time (assuming no conflict) is independent of the module being accessed (uniform Memory access).

#### Computation Gap — Multiprocessor Systems

- Loosely Coupled: each processor has a localpublic memory.

- Each processor can directly access its memory module, but all other accesses to non-local memory modules must be made through an interconnection network (non-uniform memory access).

Computation Gap — Multiprocessor Systems

Besides the higher throughput, multiprocessor systems offer more reliability since failure in any one of the redundant components can be tolerated through system reconfiguration.

## Computation Gap — Multiprocessor Systems

Multiprocessor organization is a logical extension of the parallel system - i.e., array of processor organization.

However, the degree of freedom associated with the processors are much higher than it is in an array processor.

## Computation Gap — Multiprocessor Systems

The independence of the processors and the sharing of resources among the processors - both desirable features - are achieved at the expense of an increase in complexity at both the hardware and software levels.

Computation Gap — Pipeline Systems

\*The term pipelining refers to a design technique that introduces concurrency by taking a basic function to be involved repeatedly in a process and partitioning it into several sub-functions with the following properties:

## Computation Gap — Pipeline Systems

- Evaluation of the basic function is equivalent to some sequential evaluation of the subfunctions.

- Other than the exchange of inputs and outputs, there is no interrelationships between subfunctions.

- Hardware may be developed to execute each sub-function.

- The execution time of these hardware units are usually approximately equal.

Computation Gap — Pipeline Systems

\*The concept of pipelining can be implemented at different levels. With regard to this issue, one can then address:

Arithmetic Pipelining

Instruction Pipelining

Processor Pipelining

## Computation Gap — Pipeline Systems

#### Pipeline systems can be further classified as:

- Linear Pipe

- Feedback Pipe

- Scalar Pipe

- Vector Pipe

- Unifunction Pipe

- Multifunction Pipe

- Statically Configured Pipe

- Dynamically Configured Pipe

Computation Gap — Pipeline Systems

Example

•Calculate the speed-up factor for in a multifunction pipe of 5 stages, where A and B are two one dimensional arrays of N elements.

V =  $\sum_{i=1}^{N} A(i) * B(i)$

# ◆ Computation Gap — Pipeline Systems \* Example Product terms will be generated in (n-1)+5 steps. Additions will be performed in 5+([n/2]-1)+5+([n/4]-1)+...+5+(1-1) ≅ (4log2n+n) steps. Speed-up ratio

$$S = \frac{5(2n-1)}{2n+4 \log_2 n+4} \approx 5 \text{ for large n}$$

## Parallelism vs. Pipelining

- Both techniques attempt to increase the performance.

- Parallelism is achieved through the replication of basic hardware, while pipelining is the result of staging the hardware unit.

- In general, parallelism is more reliable than pipelining.

- Parallelism is more extendable than pipelining.

- The difference between the two schemes also shows up in memory organization, bandwidth, internal interconnection and control.

## Shortcomings of the Concurrent Control Flow Systems

- Complexity: This is mainly due to the simultaneous competition/cooperation of several modules over common resources. This leads to more complexity and sophistication at the control structure and interconnection network.

- Specialization: Control flow concurrent systems require specialized and different programming skills for efficient resource utilization.

## Shortcomings of the Concurrent Control Flow Systems

- Semantic Gap: Control flow concurrent systems offer a wider semantic gap than their sequential predecessors.

- Lack of suitable parallel algorithms for various applications.

- Lack of suitable parallel high level languages to allow the programmer to express parallelism explicitly in the problem being encoded.

# Shortcomings of the Concurrent Control Flow Systems

- Lack of suitable compilation techniques to detect embedded parallelism in a sequential program.

- Lack of suitable control algorithms to distribute hardware resources among concurrently running programs.

# Shortcomings of the Concurrent Control Flow Systems — Example

\*Let us compute

$$y = \sum_{i=1}^{N} A(i) * B(i)$$

## Shortcomings of the Concurrent Control Flow Systems — Example

- In Parallel System assuming that the operands are properly aligned and only a subset of processor which handle these operands become active at successive iterations:

- Product terms could be generated in parallel in one step.

- Additions will be performed in log<sub>2</sub>N iterations.

Speed up ratio  $S = \frac{2N-1}{\approx 0} \sum_{n=1}^{\infty} S_{n}$  s achieved at the expense of poor  $1 + \log_2 N$   $\log_2 N$

resource utilization.

# Shortcomings of the Concurrent Control Flow Systems — Example

- In Pipeline System assuming a multi-function pipe of 5 stages and availability of a constant flow of data to the pipe:

- Product terms will be generated in (N-1)+5 steps.

- Additions will be performed in

$5 + \left( \left\lceil \frac{N}{2} \right\rceil - 1 \right) + 5 + \left( \left\lceil \frac{N}{4} \right\rceil - 1 \right) + \dots + 5 + (1 - 1) \le 4 \log N + N \text{ steps}$

Speed up ratio

$$S = \frac{5(2N-1)}{2N+4\log N+4} \approx 5$$