# Computer Organization MIPS Architecture

Department of Computer Science Missouri University of Science & Technology hurson@mst.edu

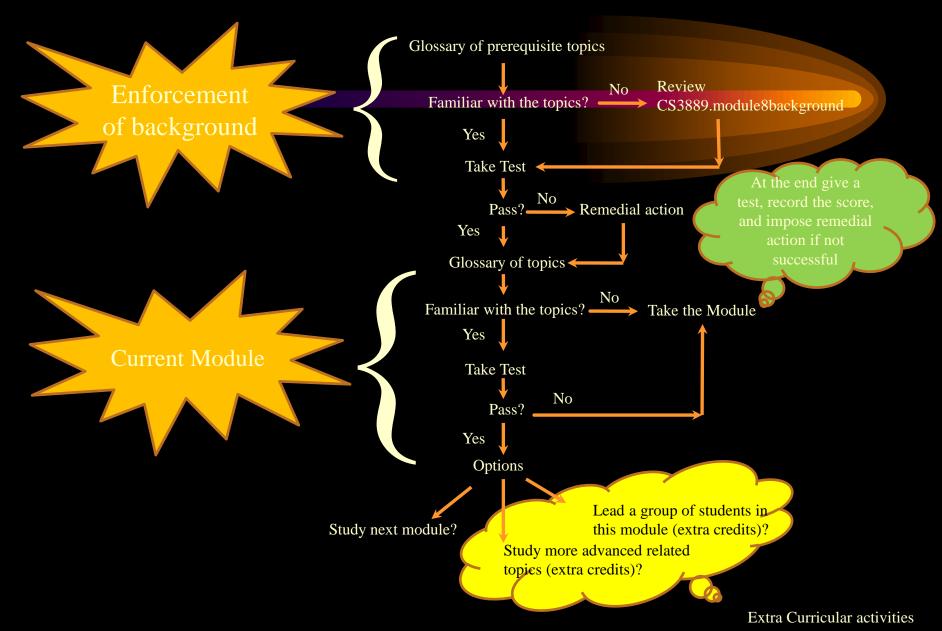

Note, this unit will be covered in three lectures. In case you finish it earlier, then you have the following options:

- 1) Take the early test and start CS3889.module9

- 2) Study the supplement module (supplement CS3889.module88)

- 3) Act as a helper to help other students in studying CS3889.module8

Note, options 2 and 3 have extra credits as noted in course outline.

MIPS – Microprocessor without Interlocked Pipeline Stages

- MIPS processors (R2000 and R3000) have 5stage pipeline, R4000 and R4400 have 8-stage pipeline, and the number of pipeline stages for R10000 varies, based on the functional units through which the instruction must pass:

- Integer instructions 5 stages

- Load/Store 6 stages

- •Floating point 7 stages.

MIPS — Microprocessor without Interlocked Pipeline Stages

- ★First MIPS instruction set architecture was MIPS I followed by MIPS II-MIPS V.

- The current MIPS instruction set architecture is referred to as MIPS32 (for 32-bit architecture) and MIPS64 (for 64-bit architecture).

★MIPS32 has 168 32-bit instructions.

General Configuration \*A word addressable, 3-address machine \*A Load/Store instruction set **\***Register Mode Operations **★**32 32 bits registers **\***Byte Addressable Main memory \*Main memory is of size  $2^{30} * 32$ \*Fixed instruction length of 32 bits

- **\***MIPS Supports:

- Register,

- Base or displacement (Index)

- Immediate

- PC relative, and

- Pseudo direct addressing modes

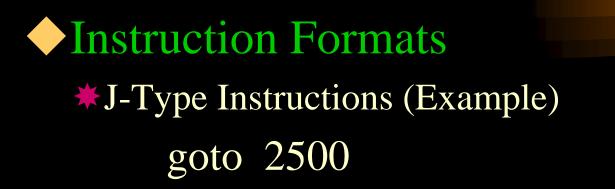

- \*MIPS Supports 3 different instruction formats:

- R (Register) Type

- I (Immediate) Type

- J (Jump) Type

# Register Configuration

| Name                             | Register no. | Usage            |

|----------------------------------|--------------|------------------|

| \$zero                           | 0            | Constant zero    |

| \$v <sub>0</sub> -v <sub>1</sub> | 2-3          | Return values    |

| \$a <sub>0</sub> -a <sub>3</sub> | 4-7          | Input parameters |

| $t_0 - t_7$                      | 8-15         | Temporary Values |

| \$s <sub>0</sub> -s <sub>7</sub> | 16-23        | Saved Values     |

| $t_8 - t_9$                      | 24-25        | Temporary Values |

| \$gp                             | 28           | Global pointer   |

| \$sp                             | 29           | Stack pointer    |

| \$fp                             | 30           | Frame pointer    |

| \$ra                             | 31           | Return address   |

#### Register Configuration

- \*Register zero  $(r_0)$  is hard-wired to a value of zero,

- \* $r_{31}$  is the default register for use with certain instructions i.e., it is used as implied mode,

- \* $r_1$  is reserved,  $r_{26}$  and  $r_{27}$  are used by the operating system.

### Addressing Modes

- •Register addressing: operand is a register

- Base or displacement (Index): operand is at the memory location whose address is the sum of a register and a constant specified in the instruction

- •Immediate: operand is a constant defined in the instruction

- PC relative: the address is the sum of the PC and a constant defined in the instruction

- Pseudo direct addressing: the address is the 26 bits of the value defined in the instruction concatenated with the upper 4 bits of PC.

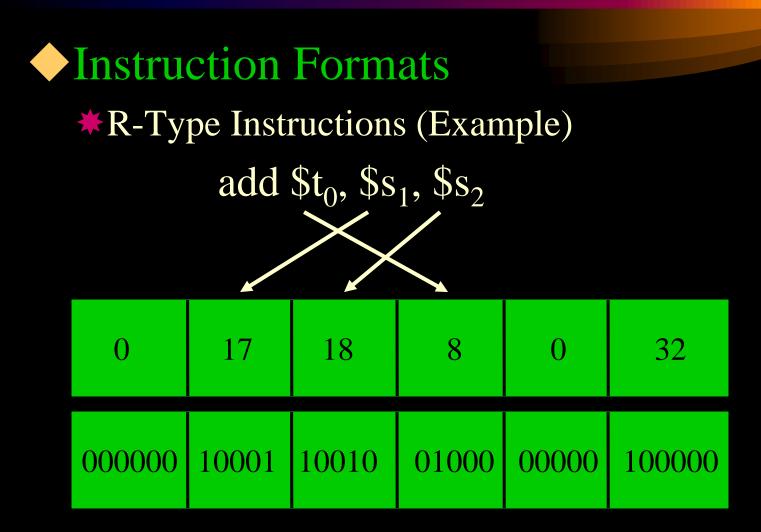

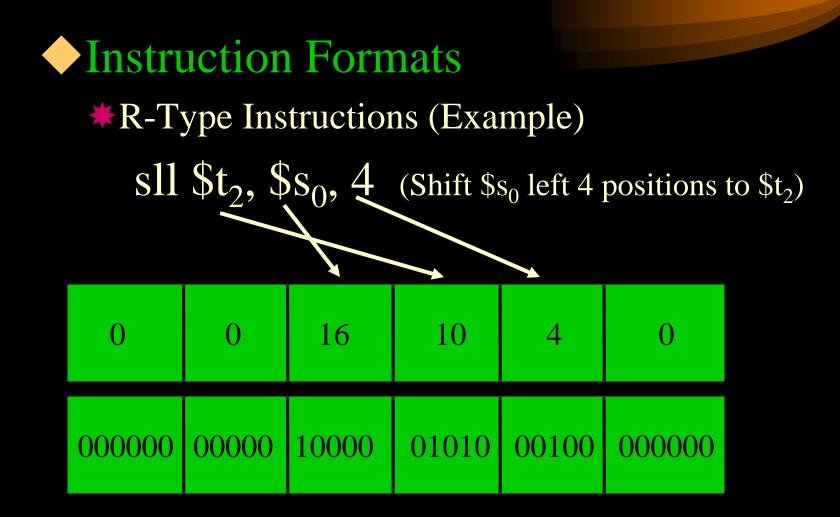

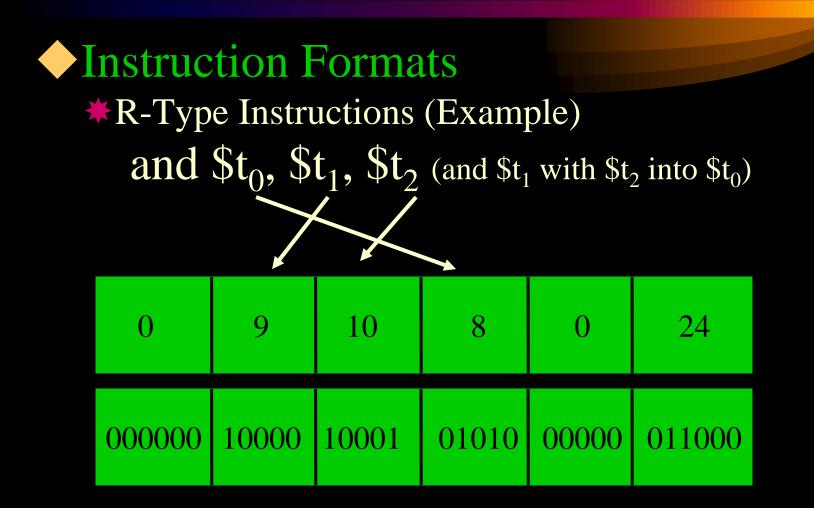

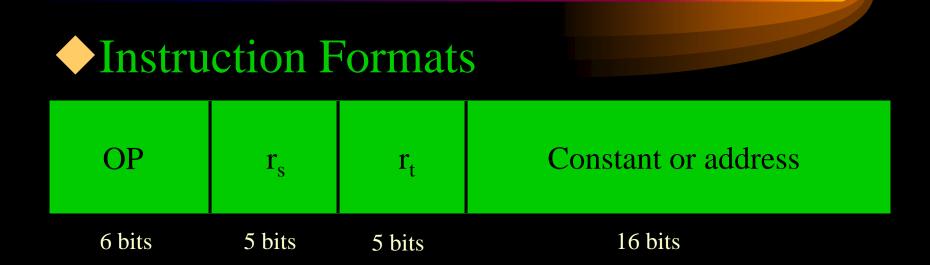

| Instruction Formats |                |                |                |        |        |

|---------------------|----------------|----------------|----------------|--------|--------|

| OP                  | r <sub>s</sub> | r <sub>t</sub> | r <sub>d</sub> | Shamt  | Funct  |

| 6 bits              | 5 bits         | 5 bits         | 5 bits         | 5 bits | 6 bits |

- OP: Basic operation code: op code

- $r_s$ : 1<sup>st</sup> source register

- $r_t$ : 2<sup>nd</sup> source register

- r<sub>d</sub>: destination register

- Shamt: Shift amount

- Funct: Function code: modifier to op code.

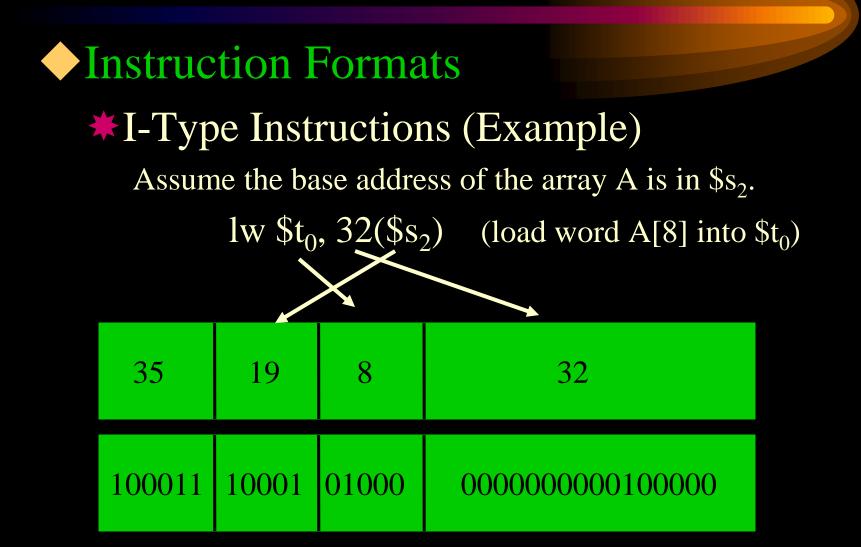

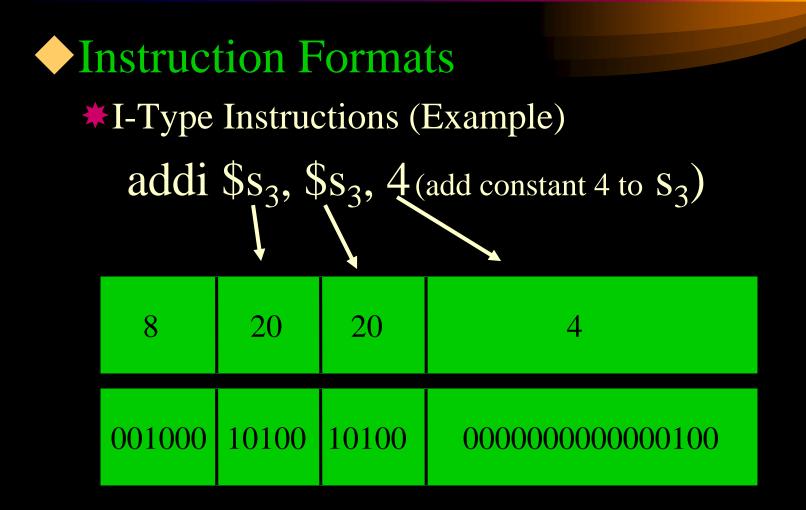

•OP: Basic operation code: op code

- $\bullet$ r<sub>s</sub>: base (index) register

- •r<sub>t</sub>: source/destination register

Instruction Formats – Assembly code

\*If \$t<sub>1</sub> has the base for the array A and \$s<sub>2</sub> corresponds to h, then write an assembly code for:

A[300] = h + A[300]  $lw \ \$t_0, \ 1200(\ \$t_1)$ add \ \\$t\_0, \ \\$s\_2, \ \\$t\_0  $sw \ \$t_0, \ 1200(\ \$t_1)$

# ◆Instruction Formats — Machine code

| 35 | 9  | 8 |      | 1200 |    |

|----|----|---|------|------|----|

| 0  | 18 | 8 | 8    | 0    | 32 |

| 43 | 9  | 8 | 1200 |      |    |

# Instruction Formats – Machine code (Binary)

| 100011 | 01001 | 01000 | 0000010010110000 |       |        |

|--------|-------|-------|------------------|-------|--------|

| 000000 | 10010 | 01000 | 01000            | 00000 | 100000 |

| 101011 | 01001 | 01000 | 0000010010110000 |       |        |

•OP: Basic operation code: op code

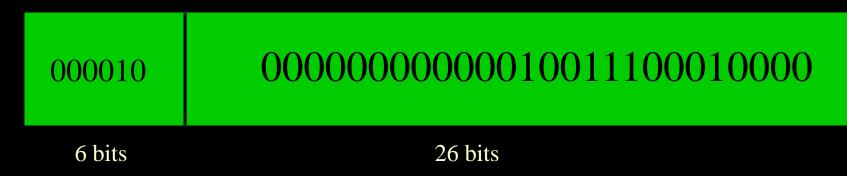

Instruction Formats **\*** If (i = = j) f = g + h; else f = g - h; \*Assuming *i* is in  $S_3$ , *j* is in  $S_4$ , *g* is in  $S_1$ , and h is in  $S_2$ . bne  $\$s_3$ ,  $\$s_4$ , Else goto Else if  $i \neq j$ add  $\$s_0, \$s_1, \$s_2$  f = g + hi Exit Else: Sub  $\$s_0, \$s_1, \$s_2$  f = g - hExit:

Assume *Save* is an array whose base is in  $\$s_6$ . Also assume *i* and *k* correspond to registers  $\$s_3$  and  $\$s_5$ , respectively;

# Instruction Formats

Exit:

# Instruction Formats

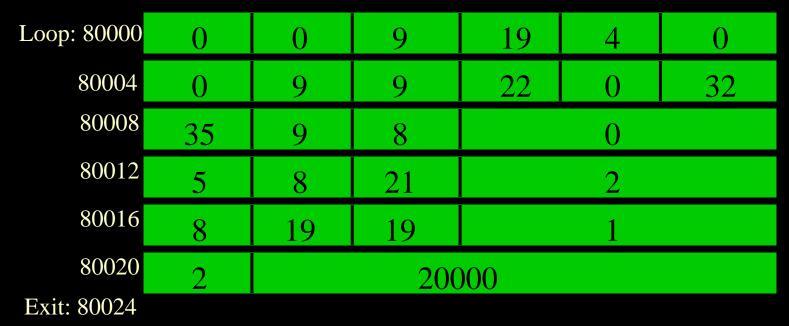

★In the previous example, if the loop is starting at location 80,000, then what is the MIPS machine code:

Load Upper Immediate (lui) sets the upper 16 bits of a constant in a register

| lui | \$t <sub>0</sub> , | 255 |

|-----|--------------------|-----|

|-----|--------------------|-----|

001111 00000 01000 0000 0000 1111 1111

\*After execution  $t_0$  is:

0000 0000 1111 1111

$0000 \ 0000 \ 0000 \ 0000$

$0000 \ 0000 \ 0011 \ 1101 \ 0000 \ 1001 \ 0000 \ 0000$

lui  $\$s_0, 61$ ori  $\$s_0, \$s_0, 2304$

- \*A procedure is a sequence of instructions that performs a specific task based on its input parameters.

- \*In the execution of a procedure, the program performs the following steps:

- Place input parameters in a place where it is accessible by the procedure,

- Transfer control to the procedure,

- Acquire the storage resources for the procedure,

- Execute the procedure,

- Place the result in a place accessible to the calling program,

- Return control to the point of origin.

#### **★**In MIPS:

- $a_0$ - $a_3$  are used to pass parameters,

- $v_0$ - $v_1$  are used to return values,

- $r_a$  is used to return to the point of origin.

- The Jump-and-link instruction (jal) saves the return address and jump to the define address:

- jal Procedureaddress

- The Jump-register (jr) instruction returns the control to the point of origin:

- jr \$r<sub>a</sub>

#### ♦Procedure

\* Assume the following subroutine was called: Int leaf\_example (int g, int h, int i, int j) Int f; F = (g + h) - (I + j)Return f;

\*The parameters g, h, i, and j are input parameters and f is the return value.

\*If this program is compiled for MIPS then we have:

### Procedure

- \*The parameters g, h, i, and j correspond to  $a_0^$  $a_3$ , and f corresponds to  $s_0$ .

- \*The compiled program starts with the label "leaf\_example".

- Internally the procedure will use some of the registers (working registers) during the execution time, as a result, the contents of these registers must be saved and restore after the execution of the subroutine. This will be done in the system stack.

#### Procedure

- **★** addi \$sp, \$sp, -12 sw  $$t_1, 8($sp)$ \***\*** sw  $$t_0, 4(\$sp)$ \* sw  $$s_0, 0($sp)$ \* add  $$t_0, $a_0, $a_1$ \* add  $$t_1, $a_2, $a_3$ \* sub  $$s_0, $t_0, $t_1$ \* add  $\$v_0$ ,  $\$s_0$ , \$zero\* lw \$s<sub>0</sub>, 0(\$sp) \* lw \$t<sub>0</sub>, 4(\$sp)  $* lw $t_1, 8($sp)$ **★** addi \$sp, \$sp, 12 **∗** jr \$ra callee#

- # The first four instructions allow us to save the contents of the working registers in the stack#

- #This instruction and the next three instructions are intended to restore the original contents of the working registers before control transfers to the callee procedure#

- #This instruction transfers the control back to

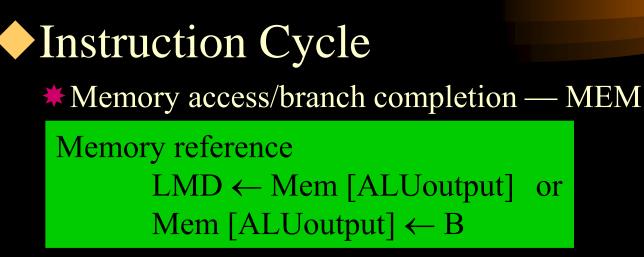

\*An instruction cycle is implemented in five basic steps:

Instruction Fetch — IF IR  $\leftarrow$  Mem [PC] NPC  $\leftarrow$  PC + 4

Instruction decode and register fetch — ID  $A \leftarrow \text{Regs} [IR_{6,..,10}]$   $B \leftarrow \text{Regs} [IR_{11,..,15}]$  $\text{Imm} \leftarrow ((IR_{16})^{16} \# \# IR_{16...31})$

\* Execution and effective address calculation — EX

Memory reference ALUoutput  $\leftarrow A + Imm$ Reg.-Reg. ALU instruction ALUoutput  $\leftarrow A$  op-code B Reg.-Immediate ALU instruction ALUoutput  $\leftarrow A$  op-code Imm Branch ALUoutput  $\leftarrow NPC + Imm$ , Cond  $\leftarrow (A \text{ op-code } 0)$

Branch

If (cond.)  $PC \leftarrow ALU$ output else  $PC \leftarrow NPC$

Reg.-Reg. ALU instruction Regs  $[IR_{16,..,20}] \leftarrow ALUoutput$

Reg.-Immediate ALU instruction Regs  $[IR_{11,..,15}] \leftarrow ALUoutput$

Load instruction Regs  $[IR_{11,...,15}] \leftarrow LMD$

# Pipelined instruction cycle

Inst. i EX MEM WB IF ID Inst. i+1 EX MEM WB IF ID Inst. i+2 IF ID EX MEM WB Inst. i+3  $\mathbf{IF}$ ID EX MEM WB

A pipelined instruction cycle gives a peak performance of one instruction every step.