## Arithmetic Logic Unit

A.R. Hurson Department of Computer Science Missouri University of Science & Technology

#### Arithmetic Logic Unit

- It is a functional box designed to perform "basic" arithmetic, logic, and shift operations on the data.

- Implementation of the basic operations such as logic, program control, and data transfer operations are easier than arithmetic and I/O operations. Therefore, in this section we concentrate on arithmetic operations.

#### Arithmetic Logic Unit

- For a simple machine, the ALU should at least be able to perform operations such as:

- add

- increment

- subtract

- decrement

- •

- •

- •

- A simple ALU is basically an adder and some control circuits augmented by special circuits to carry out the logic and shift operations.

- Arithmetic Logic Unit

- An ALU can be of three types:

- Serial

- Parallel

- Functional (Modular)

#### Arithmetic Logic Unit

- Similar to the definition of serial and parallel adders, one can define serial and parallel ALUs.

- In a serial ALU during each clock pulse one bit of operand(s) participates in the operation.

- In a parallel ALU operation on all the bits of operand(s) is initiated simultaneously.

- In a simple word a parallel ALU can be looked at as a cascade of identical units forming a one dimensional array of cells.

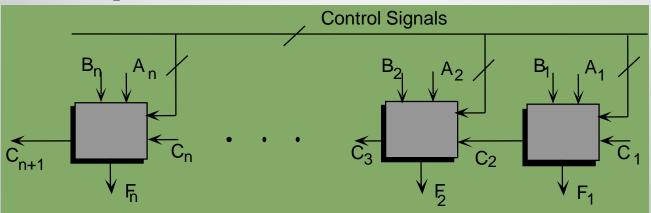

- Arithmetic Logic Unit Parallel ALU

- ALU operation is determined by the control signals.

- In a very simple form, the bit-pattern of the control signals is determined by the operation code.

- In a parallel ALU, one needs to determine the design of a unit and then replicate it.

- Arithmetic Logic Unit Parallel ALU (Example)

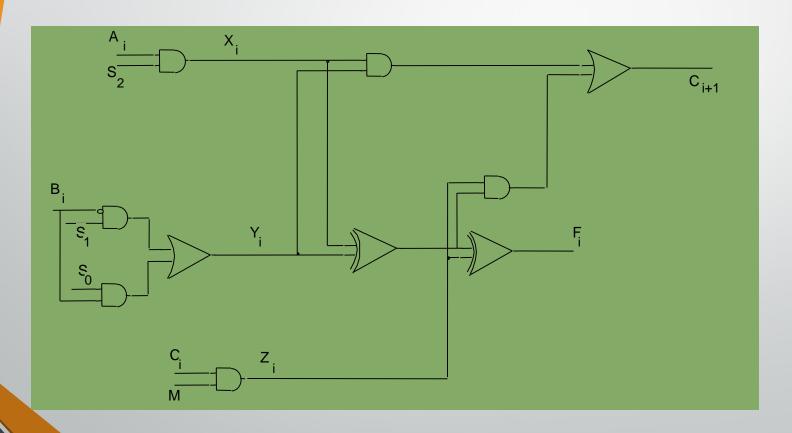

- $\bullet$  S<sub>2</sub>, S<sub>1</sub>, S<sub>0</sub>, and M are the control signals.

- $\bullet$  A<sub>i</sub>, B<sub>i</sub>, and C<sub>i</sub> are the operand bits and carry-in, respectively.

- $F_i$  and  $C_{i+1}$  are the result bit and carry-out, respectively.

- Arithmetic Logic Unit Parallel ALU (Example)

- The function of each stage can be defined as:

$$F_i = X_i \oplus Y_i \oplus Z_i$$

$$C_{i+1} = X_iY_i + (X_i \oplus Y_i)Z_i = X_iY_i + X_iZ_i + Y_iZ_i$$

By appropriate setting of the control signals one can initiate a variety of the operations.

Arithmetic Logic Unit — Parallel ALU (Example)

$C_1 = 0$

$$M = 0$$

$S_2 = 1$

$S_1 = 1$

$S_0 = 1$

$M = 1$

$S_2 = 1$

$S_1 = 1$   $\Rightarrow F \leftarrow A - 1$

$S_0 = 1$

#### Arithmetic Logic Unit

- As discussed before a parallel ALU offers a higher speed relative to a serial ALU.

- How can one improve the performance (speed) of ALU further? In other words; is it possible to build (design) an ALU faster than a parallel ALU?

- Arithmetic Logic Unit Functional (modular) ALU

- In this model, ALU is a collection of independent units each tailored (specialized) for a specific operation. As a result, execution of independent operations can be overlapped.

- This approach allows an additional degree of concurrency relative to a parallel ALU, since it allows several operations to be performed on data simultaneously.

- However, this speed improvement comes at the expense of extra overhead which is needed to detect data independent operations.

• Arithmetic Logic Unit — Functional (modular) ALU

| Adder <sub>1</sub> | Adder <sub>2</sub> | Subtractor |

|--------------------|--------------------|------------|

| Multiplier         |                    |            |

- Arithmetic Logic Unit Question

- Is it possible to improve the performance of an ALU further?

- Naturally, we can improve performance (physical speed) by taking advantage of the advances in technology.

- How can we improve the logical speed of the ALU further?

- In a functional ALU, is it possible to devise algorithms which allow one to improve the performance of the basic operations?

- If this is a valid direction, then the question of "How to design a fast ALU?" will change to "How to design a fast adder, a fast multiplier, ...?"

#### • Arithmetic Logic Unit — Arithmetic Algorithm

- The goal is to develop a set of algorithms which allow the execution of basic arithmetic operations on data values presented in different formats and notations (i.e., fixed point, floating point, signed numbers).

- In general fixed point operations are easier and faster than floating point operations.

- Signed numbers could be in signed magnitude or signed complement format.

**Arithmetic Logic Unit** – Comparison of 2-Unsigned Numbers (Direct Comparison)

• Two binary bits (a, b) are equal iff:

$$x = (a \land b) \lor (\overline{a} \land \overline{b}) = 1$$

Consequently two registers of n-bits are equal iff:

$$x = x_{n-1} \land x_{n-2} \land \ldots \land x_0 = 1$$

where  $x_i = A_i \odot B_i$   $0 \le i \le n-1$

In other words

$$A = B \Rightarrow x = \bigwedge_{i=0}^{n-1} x_i = 1$$

- Arithmetic Logic Unit Comparison of 2-Unsigned Numbers (Direct Comparison)

- Similarly

$$A > B \Rightarrow A_{n-1} \overline{B}_{n-1} + X_{n-1} A_{n-2} \overline{B}_{n-2} + ... + X_{n-1} X_{n-2} ... X_1 A_0 \overline{B}_0 = 1$$

$$A \leq B \Rightarrow A_{n-1}B_{n-1} + X_{n-1}A_{n-2}B_{n-2} + ... + X_{n-1}X_{n-2} ... X_1A_0B_0 = 1$$

- Arithmetic Logic Unit Comparison of 2-Unsigned Numbers (Direct Comparison)

- Example:

$$\mathbf{x}_6 \wedge \mathbf{x}_5 \wedge \mathbf{x}_4 \wedge \mathbf{x}_3 \wedge \mathbf{x}_2 \wedge \mathbf{x}_1 \wedge \mathbf{x}_0 = \mathbf{1} \wedge \mathbf{1} \wedge \mathbf{1} \wedge \mathbf{0} \wedge \mathbf{0} \wedge \mathbf{0} \wedge \mathbf{0} = \mathbf{0} \Longrightarrow \mathbf{A} \neq \mathbf{B}$$

$$x6 \wedge x5 \wedge x4 \wedge x3 \wedge x2 \wedge x1 \wedge x0 = 1 \wedge 1 \wedge 1 \wedge 0 \wedge 0 \wedge 0 \wedge 0 \wedge 0 = 0$$

$$\Rightarrow A \neq B$$

$$A_{6} \overline{B}_{6} + x_{6} A_{5} \overline{B}_{5} + x_{6} x_{5} A_{4} \overline{B}_{4} + x_{6} x_{5} x_{4} A_{3} \overline{B}_{3} + x_{6} x_{5} x_{4} x_{3} A_{2} \overline{B}_{2} + x_{6} x_{5} x_{4} x_{3} x_{2} A_{1} \overline{B}_{1} + x_{6} x_{5} x_{4} x_{3} x_{2} x_{1} A_{0} \overline{B}_{0} = 0 + 0 + 0 + 0 + 0 + 0 + 0 = 0$$

$$\Rightarrow A \Rightarrow B$$

$$B_{6} \overline{A}_{6} + x_{6} B_{5} \overline{A}_{5} + x_{6} x_{5} B_{4} \overline{A}_{4} + x_{6} x_{5} x_{4} B_{3} \overline{A}_{3} + x_{6} x_{5} x_{4} x_{3} B_{2} \overline{A}_{2} + x_{6} x_{5} x_{4} x_{3} x_{2} B_{1} \overline{A}_{1} + x_{6} x_{5} x_{4} x_{3} x_{2} x_{1} B_{0} \overline{A}_{0} = 0 + 0 + 0 + 1 + 0 + 0 + 0 = 1$$

$$\Rightarrow A < B$$

19

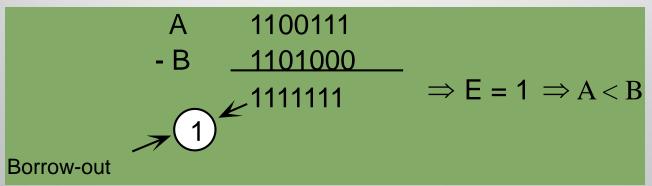

- Arithmetic Logic Unit Comparison of 2-Unsigned Numbers (Direct Subtraction)

- Assume E is the borrow-out of a parallel subtractor then:

if

$$A \ge B$$

then  $E = 0$

if

$$A < B$$

then  $E = 1$

if

$$A = B$$

then  $E = 0$  and result all 0s

In other words, to check the relative magnitude of two unsigned numbers say, *A* and *B*. Perform A-B and then check the borrow-out. The relative magnitude of *A* and *B* is determined according to the above relationships.

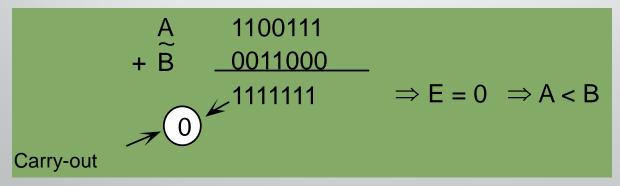

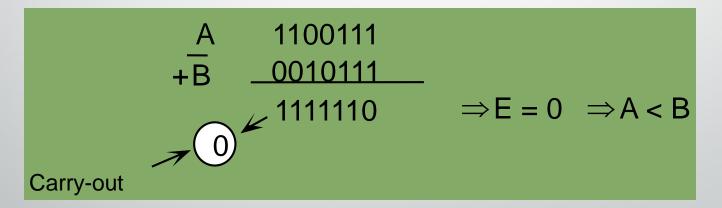

- Arithmetic Logic Unit Comparison of 2-Unsigned Numbers (2<sup>s</sup> Complement Addition)

- Assume E is the carry-out of a parallel adder then:

```

if A < B then E = 0

```

if  $A \ge B$  then E = 1

if A = B then E = 1 and result all 0s

**Arithmetic Logic Unit** – Comparison of 2-Unsigned Numbers (2<sup>s</sup> Complement Addition)

Proof:

$$A - B = A + \widetilde{B} = A + 2^{n} - B = 2^{n} + A - B$$

- if  $A \ge B \Rightarrow A B \ge 0 \Rightarrow 2^n + A B \ge 2^n \Rightarrow E = 1$

- if  $A < B \Rightarrow A B < 0 \Rightarrow 2^n + A B < 2^n \Rightarrow E = 0$

- if  $A = B \Rightarrow A B = 0 \Rightarrow 2^n + A B = 2^n \Rightarrow E = 1$  and result all  $0^s$

- To determine the relative magnitude of two unsigned numbers, perform  $A + \tilde{B}$  and then check the carry-out.

# **Arithmetic Logic Unit** – Comparison of 2-Unsigned Numbers (1<sup>s</sup> Complement Addition)

Assume E is the carry-out of a parallel adder then:

if

$$A \le B$$

then  $E = 0$

if A = B then E=0 and result all 1s

if

$$A > B$$

then  $E = 1$

To determine the relative magnitude of two unsigned numbers, perform  $A + \overline{B}$  and then check the carry-out.

A.R. Hurson

23

- Arithmetic Logic Unit Comparison of 2-Unsigned Numbers (Direct Subtraction)

- Example

- Arithmetic Logic Unit Comparison of 2-Unsigned Numbers (2<sup>s</sup> Complement Addition)

- Example

- Arithmetic Logic Unit Comparison of 2-Unsigned Numbers (1<sup>s</sup> Complement Addition)

- Example

A.R. Hurson

26

#### Questions

- Prove the aforementioned formulas for the 1<sup>s</sup> complement addition operation.

- How can one determine the relative magnitude of signed numbers?

A.R. Hurson

27

- **Arithmetic Logic Unit** Addition Algorithm (2<sup>s</sup> Complement Numbers)

- Add numbers including the sign bits. If there is a carry-out of the last digit, then disregard it.

- **Arithmetic Logic Unit** Addition Algorithm (1<sup>s</sup> Complement Numbers)

- Add numbers including the sign bits. If there is a carry-out then increment the result by 1 (wrap around the carry).

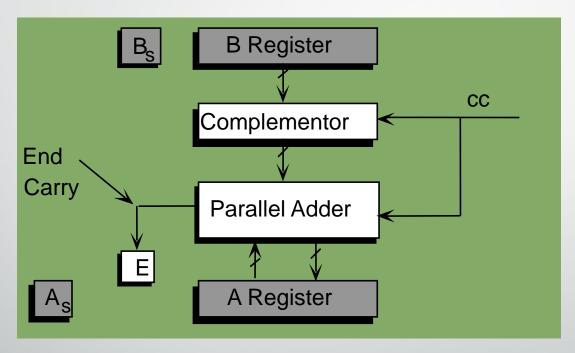

- Arithmetic Logic Unit Addition Algorithm (Signed magnitude numbers)

- Addition (Subtraction):

- When the signs of numbers (say A and B) are identical (different) add the two magnitudes. Sign of the result is the same as A.

- When the signs of A and B are different (identical), compare the magnitudes and subtract the smaller magnitude from the larger one. Sign of the result is the same as the sign of the larger magnitude.

- If result zero then set the sign of the result to 0.

- Arithmetic Logic Unit Addition Algorithm (Signed magnitude numbers)

- How to reduce hardware requirements of the proposed algorithm?

- Subtraction can be converted into addition.

- Magnitudes can be compared using an adder.

Arithmetic Logic Unit – Addition Algorithm (Signed magnitude numbers)

- cc = 0 if (addition and  $A_s = B_s$ ) or (subtraction and  $A_s \neq B_s$ )

- cc = 1 if (addition and  $A_s \neq B_s$ ) or (subtraction and  $A_s = B_s$ )

- Arithmetic Logic Unit Addition Algorithm (Signed magnitude numbers)

- Example

$$A (+29)$$

$\Rightarrow$  0011101  $\Rightarrow$  Same signs and addition  $+B (+14)$   $\Rightarrow$  Same signs and addition  $+B (+14)$   $\Rightarrow$  Add the magnitudes.  $+B (+14)$   $\Rightarrow$   $+D (+14)$   $\Rightarrow$  Same signs and addition  $+D (+14)$   $\Rightarrow$  Same signs and addi

- Arithmetic Logic Unit Addition Algorithm (Signed magnitude numbers)

- Example

$$A (-14) \Rightarrow 101110 \\ +B (-7) \Rightarrow + 100111 \Rightarrow Same signs and addition$$

$$01110 \\ 00111 \\ E \\ 10101 \qquad E = 0$$

$$A = 110101 \quad Final result (-21).$$

- Arithmetic Logic Unit Addition Algorithm (Signed magnitude numbers)

- Example

```

A (-14) \Rightarrow 101110 \\ -B (-7) \Rightarrow -100111 \Rightarrow Same signs and subtract

01110 \\ 11001 \\ E \\ 00111 \qquad Add 2^s complete of B to A.

E = 1, A>B

A = 100111 \quad Final result (-7).

```

- Arithmetic Logic Unit Addition Algorithm (Signed magnitude numbers)

- Example

```

A (+14) \Rightarrow 001110 \\ -B (+20) \Rightarrow -010100 \Rightarrow Same signs and subtract

01110 \\ 01100 \\ E \\ 00111 \\ O = 001110 \\ O = 00111 \\ O = 001110 \\ O = 001

```

Arithmetic Logic Unit – Addition Algorithm (Signed magnitude numbers)

Example

- Arithmetic Logic Unit Addition Algorithm (Signed magnitude numbers)

- Example

```

A \Rightarrow 111011 \Rightarrow Different signs and addition

11011 \Rightarrow Take 2<sup>s</sup> complement of B and add.

11010 \Rightarrow E = 1 and result \Rightarrow A > B

A = 110100 Final result.

```

- Arithmetic Logic Unit Addition Algorithm (Signed magnitude numbers)

- Example

- Arithmetic Logic Unit Addition Algorithm (Signed magnitude numbers)

- Example

```

A 000111

B 001011 Same signs and subtraction.

O0111

10101 Take 2^s complement of B and add.

E = 0 \Rightarrow B > A

A = 100100 Final result, take 2^s complement of result.

```

- Questions

- What is an overflow?

- How can we detect overflow for:

- Signed magnitude addition?

- 1<sup>s</sup> complement addition?

- 2<sup>s</sup> complement addition?

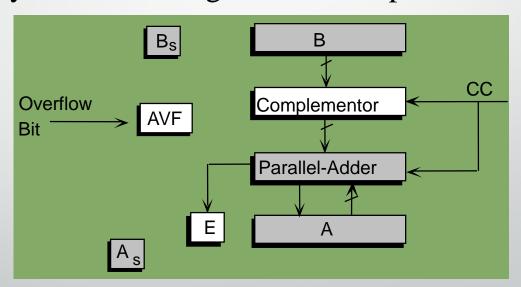

#### Arithmetic Logic Unit — Addition Overflow

- Overflow occurs when two numbers of n digits each are added and the sum occupies n+1 digits.

- An overflow cannot occur after an addition if one number is positive and the other is negative.

- In general, overflow can only occur when adding numbers of the same sign or subtracting numbers of different signs.

• Arithmetic Logic Unit — Addition Overflow (Signed magnitude numbers)

Detection of overflow in signed magnitude addition is simple. Carry-out of the magnitude bits represents an

overflow:

If (cc = 0 and E = 1) then AVF  $\Leftarrow 1$  otherwise AVF  $\Leftarrow 0$

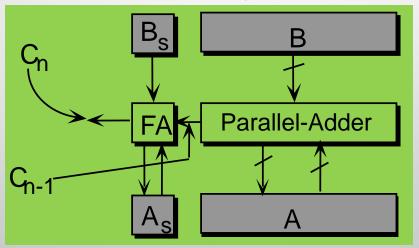

- Arithmetic Logic Unit Addition Overflow (2s Complement Numbers)

- Overflow is occurred when adding numbers of the same sign results in a number of a different sign.

Overflow occurs if  $C_n \oplus C_{n-1} = 1$

- Arithmetic Logic Unit Multiplication Algorithm

- Multiplication can be performed as a sequence of additions.

- B \* Q  $\Rightarrow$  add B, Q times

- Two general approaches have been adapted for multiplication.

- Software approach

- Hardware approach

- Arithmetic Logic Unit Multiplication Algorithm

- Software approach

$$AC \Leftarrow 0$$

;

For  $i = 1$  to Q do;

$AC \Leftarrow (AC) + (B)$ ;

End;

• Time complexity of this algorithm is 0(m) where m is the magnitude of Q.

- Arithmetic Logic Unit Multiplication Algorithm

- Software approach

- Time complexity of the algorithm can be improved if the number of iterations is based on the multiplier length:

```

\begin{split} &AC \Leftarrow 0; \\ &For \ i=1 \ to \ n \ Do; \\ &if \ Q_1=1 \ then \ C_{out} \ AC \Leftarrow (AC) + (B); \\ &AC_n...AC_2AC_1Q_n...Q_2Q_1 \Leftarrow C_{out}AC_n...AC_2AC_1Q_n \ ...Q_2; \\ &End; \end{split}

```

- Arithmetic Logic Unit Multiplication Algorithm

- Hardware Approach

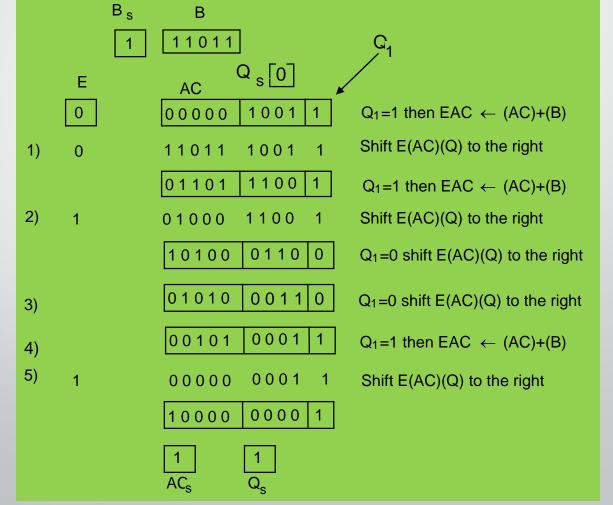

- The simplest hardware approach is based on the previous algorithm e.g., add and shift.

- In each iteration the least-significant bit of multiplier (Q) is checked;

- If one, then B is added to the accumulator and the contents of accumulator and Q is shifted right one position.

- If zero, just shift accumulator and Q to the right.

- Arithmetic Logic Unit Multiplication Algorithm (Signed magnitude numbers)

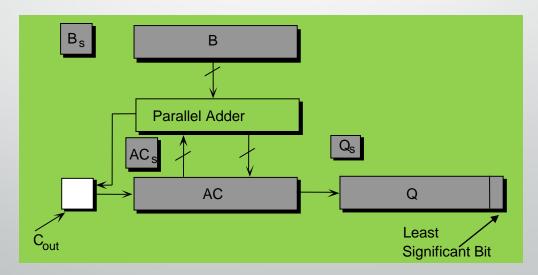

- Hardware Configuration

- A double register (AC and Q) holds the final result.

- Sign of the result is the EX-OR of the signs of multiplier and multiplicand.

- Arithmetic Logic Unit Multiplication Algorithm (Signed magnitude numbers)

- Example

- Arithmetic Logic Unit Multiplication Algorithm (2<sup>s</sup> Complement numbers)

- Pre-Post Complementation

- Convert negative numbers to positive numbers.

- Apply "add and shift" algorithm.

- Convert the result if necessary.

- Arithmetic Logic Unit Multiplication Algorithm (2<sup>s</sup> Complement numbers)

- Extension of "add and shift"

- Convert the multiplier to a positive number i.e., if multiplier is negative then multiply the multiplier and the multiplicand by -1.

- Apply a modified "add and shift" algorithm in which addition and shift operations are done for 2<sup>s</sup> complement numbers.

- **Arithmetic Logic Unit** Multiplication Algorithm (2<sup>s</sup> Complement numbers)

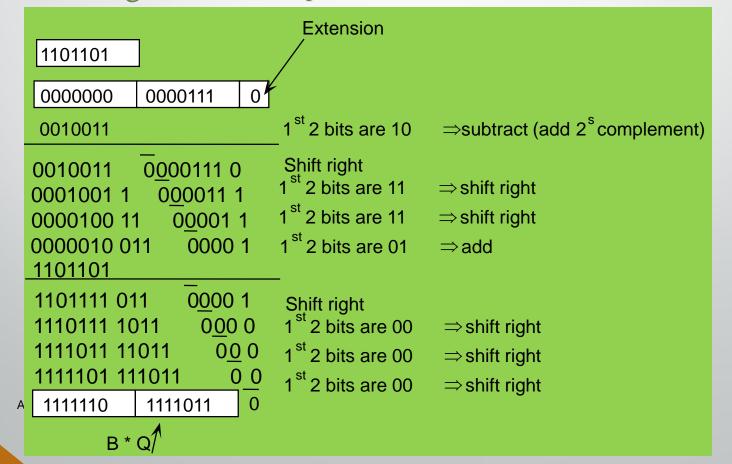

- Booth's Algorithm

- Instead of checking one bit of the multiplier at a time, check two bits at a time and take proper actions according to the following table:

- 00 no action, shift right.

- 01 add multiplicand, shift right.

- 10 subtract multiplicand, shift right.

- 11 no action, shift right.

- Arithmetic Logic Unit Multiplication Algorithm (2<sup>s</sup> Complement numbers)

- Booth's Algorithm

- It is suitable for 2<sup>s</sup> complement numbers.

- On average, Booth's Algorithm is faster than "add and shift".

- Always, extend the multiplier by a zero on the right.

- **Arithmetic Logic Unit** Multiplication Algorithm (2<sup>s</sup> Complement numbers)

- Booth's Algorithm (Example)

#### Questions

- Why is Booth's algorithm faster than "add and shift" algorithm (in general)?

- Why does Booth's Algorithm work?

- Arithmetic Logic Unit Division Algorithm

- Similar to multiplication, one can develop a software routine which performs division as a sequence of subtractions. Naturally, such an algorithm is very inefficient and slow.

- Arithmetic Logic Unit Division Algorithm

- Similar to the pencil and paper routine, one can develop an algorithm which performs division as a sequence of Compare, Shift, and Subtract operations.

- One should note that division in a binary system is much simpler than the division in decimal system, since the quotient digits are either 0 or 1.

- Arithmetic Logic Unit Division Algorithm

- To minimize the hardware requirements for division, we should remember that:

- Comparison can be performed via arithmetic operation(s).

- Subtraction can be performed via complement-addition.

- In other words; division requires almost the same hardware modules as multiplication does.

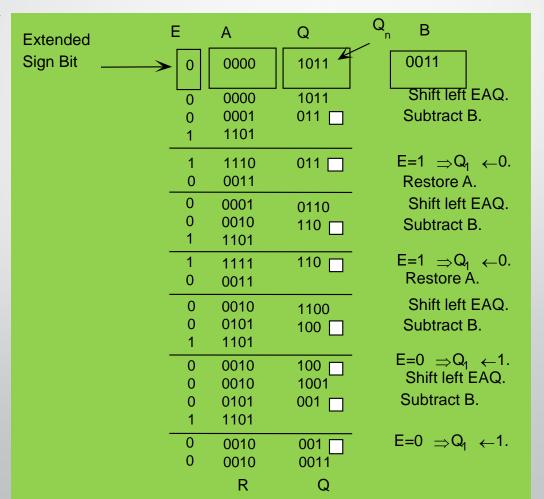

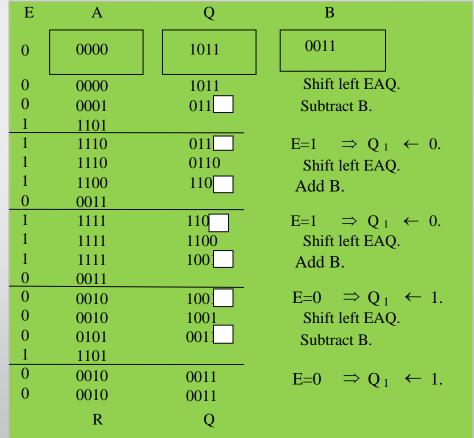

- **Arithmetic Logic Unit** Division Algorithm (Signed magnitude numbers)

- Division can be carried out as a sequence of n (n is the length of divisor) iterations.

- Dividend is a double register.

- One bit of the quotient is generated in each iteration.

- At the end of the operation, the quotient is in the 1<sup>st</sup> half part of the double register (low-order part), and remainder is in the 2<sup>nd</sup> half part.

- Sign of the quotient is the XOR of the signs of dividend and divisor.

- Sign of the remainder is the same as the sign of the dividend.

- Arithmetic Logic Unit Division Algorithm (Divide Overflow)

- In the division algorithm for signed magnitude numbers, if the 1<sup>st</sup> half part of dividend is larger than or equal to the divisor, then the quotient overflows to the remainder part. This phenomenon is called divide overflow. As a result, a wrong answer will be generated.

- To avoid divide overflow and also due to the fact that division is a time consuming operation, the divide overflow condition is checked at the beginning of the operation. In case of divide overflow, proper actions will be taken (in the form of say an interrupt).

- Arithmetic Logic Unit Methods of Division

- There are several different algorithms for division:

- Restoring Method

- Non-Restoring Method

- Direct Comparison

- Arithmetic Logic Unit Methods of Division

- Restoring Method: In the restoring method, the contents of the partial remainder is restored whenever it is detected that the divisor is larger than the partial remainder.

- Arithmetic Logic Unit Methods of Division

- Non-Restoring Method: In non-restoring method, if it is detected that the divisor is larger than the partial remainder, its contents are not restored.

- However, in the next iteration, instead of subtracting the divisor from the partial remainder, it will be added to the partial remainder.

- Arithmetic Logic Unit Methods of Division

- Direct Comparison: divisor is compared against partial remainder. If it is smaller than or equal to partial remainder, it will be subtracted and quotient digit is set to 1. Otherwise, just the quotient digit is set to zero.

- Arithmetic Logic Unit Methods of Division

- Naturally, restoring and non-restoring techniques are equivalent.

- Consider the consecutive sequence of iterations for both restoring and non-restoring techniques (next slide).

- As can be seen, both schemes generate the same value as the partial remainder. However, the non-restoring technique should be faster than the restoring method since it requires fewer number of operations.

Arithmetic Logic Unit — Methods of Division

Restoring

Subtract in the second Iteration

$$(2 ( (A-B)+B) -B) = 2A-B$$

Subtract, Restore, and Shift in the first iteration

#### Non-Restoring

Addition in the second Iteration

$$2 (A-B) +B = 2A-B$$

Subtraction and shift in the first iteration

#### Arithmetic Logic Unit – Division Algorithm (Example)

Restoring Method

#### **Arithmetic Logic Unit** — Division Algorithm (Example)

Non-restoring Method

- Arithmetic Logic Unit Floating Point Numbers

- A number *N* in base *r* can be represented in many ways. For example, decimal number 2.945 can be represented as:

$$.2945 * 10^{+1}$$

$$29.45 * 10^{-1}$$

•

•

• A scientific or floating point format of a number is a unique representation in which a number is represented as the multiple of 2 parts:

a power of the base (called exponent)\* a fraction (called mantissa)

• For example,  $+16.23 = +.1623 * 10^{+2}$

- Arithmetic Logic Unit Floating Point Numbers

- Such a representation in the computer requires two registers, one to represent the exponent and one to represent the mantissa.

- Note that each part is a signed number which could be represented in signed magnitude or signed complement format.

- A floating point number is normalized if the most significant digit of the mantissa is non-zero.

- In most systems the exponent is represented in excess base. This means positive exponent. Therefore, a fixed value (e.g., biased value) will be added to the exponent. For example, IBM uses excess 64 for the power, and DEC10 uses excess 128 to represent the power.

- Arithmetic Logic Unit Floating Point Numbers

- Convert (-25.75)<sub>10</sub> to a floating point number for IBM:

$$(-25.75)_{10} = -(11001.11)_2 = -(.11001111 * 2^5)_2 =$$

$$(.0001100111 * 2^8)_2 = -.000110011100 * 16^2$$

#### Arithmetic Logic Unit – Floating Point Addition and Subtraction

- Check for zeroes.

- Align the mantissas (smaller exponent should be equated to the larger one).

- Add or subtract the mantissas.

- Normalize the result.

- If  $\exp_1 \ge \exp_2$  then

$$fl_1 \pm fl_2 = \left( (mantissa_1) \pm (mantissa_2) * \mathbf{r}_b^{-(\exp_1 - \exp_2)} \right) * \mathbf{r}_b^{\exp_1}$$

• If  $\exp_1 < \exp_2$  then

$$fl_1 \pm fl_2 = \left( (mantissa_1) * \mathbf{r}_b^{-(\exp_2 - \exp_1)} \pm (mantissa_2) \right) * \mathbf{r}_b^{\exp_2}$$

- Arithmetic Logic Unit Floating Point Multiplication

- Check for zeros.

- Add the exponents.

- Adjust the exponent of the result.

- Multiply the mantissas.

- Normalize the result.

$$fl_1* fl_2 = (mantissa_1)* (mantissa)_2* r_b^{(exp_1 + exp_2)}$$

- Arithmetic Logic Unit Floating Point Division

- Check for zeroes.

- Align the dividend (for divide overflow condition).

- Subtract the exponents.

- Adjust the exponent of the result.

- Divide the mantissas.

$fl_1/fl_2 = (mantissa_1)/(mantissa)_2 * r_b^{(exp_1 - exp_2)}$

#### Arithmetic Logic Unit

- Singed magnitude number: A method to represent signed numbers.

- 2<sup>s</sup> complement number: A method to represent signed numbers.

- 1<sup>s</sup> complement number: A method to represent signed numbers.

- Addition overflow: A case where the addition result is too big to fit in the destination register.

#### Arithmetic Logic Unit

- Divide overflow: A case when the quotient result is too big to fit in the quotient register.

- Add-and-shift algorithm: A method to perform multiplication.

- Booth's algorithm: A method to perform multiplication for 2<sup>s</sup> complement numbers.

- Restoring technique: A method to perform division.

- Non-restoring technique: A faster method than restoring technique to perform division.

#### Arithmetic Logic Unit

- Biased value: A fixed and positive value added to the exponent of a floating point number. The goal is to deal with positive (unsigned) exponents.

- Normalized number: A floating point number is normalized if the first digit in the mantissa is a non zero digit.

- Aligning the mantissa: A process by which the mantissa is shifted to the right by the number of differences between two exponents.

- Mantissa: The fraction portion of a floating point number.

#### Questions:

- Prove that two unsigned numbers can be compared by means of 1s complement addition.

- How do we detect overflow for signed magnitude addition?

- How do we detect overflow for 2s complement addition (note I am looking for another technique than the one discussed in this unit)?

- Prove that the add-and-shift algorithm, as implemented in this unit, does not generate an overflow.

- Justify the following statement. On average, Booth's algorithm is faster than add-and-shift algorithm.

#### Questions:

- On average, Booth's algorithm is faster than add-and-shift algorithm, this means that in some cases Booth's algorithm would be slower than add-and-shift algorithm. Can you give an example that supports this?

- Add-and-shift checks one bit of multiplier during each iteration, Booth's algorithm checks two bits of multiplier during each iteration and as we discussed Booth's algorithm is faster that add-and-shift. Can you come up with an algorithm that multilies two numbers faster than Booth's algorithm?

#### Questions:

- In case of a floating point addition or subtraction operation, why should we always align the mantissa of the smaller number?

- In the case of multiplication of two floating point numbers, after adding the exponents, why should we subtract one excess base from the result?

- In the case of division of two floating point numbers, after subtracting the exponents, why should we add one excess base to the result?